Booth Multiplier Based on Low Power High Speed Full Adder With Fin_FET Technology

Main Article Content

Abstract

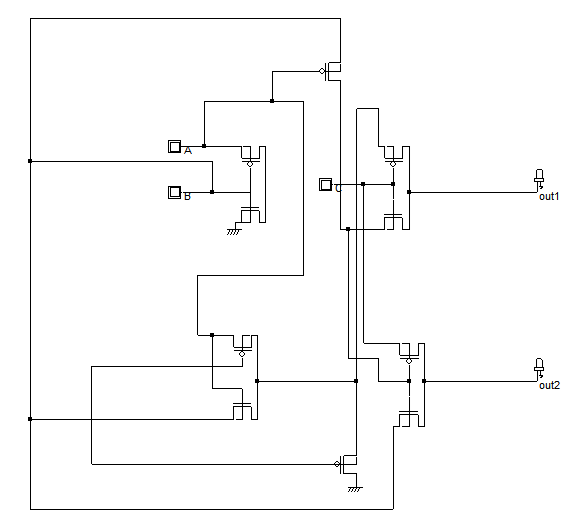

This paper proposes a novel Fin FET-based HSFA for the multiplier in order to overcome the issues of low speed operation. It is advantageous to use Fin FETs to construct the arithmetic circuit while assessing the available works. The carry propagation and slow operation of the old technique are disadvantages. The CMOS-based compressor circuit, on the other hand, suffers from leakage current, which reduces its driving capabilities. High current DSP applications are well matched to the design's specifications. Even with a supply voltage of 1 volt, the proposed device has a decent driving capability. As a result, the circuit runs more quickly and has less latency. A transmission gate is used in the design of the suggested adder structure to selectively block or transfer data from the input to output. Half adder and adder are shown in the following illustrations. The smaller the transistor count, the less power it uses. The suggested Fin FET design for the smaller transistors has a superior driving capability than the CMOS equivalent. Additionally, when cascading, the Fin FET based adder may contribute to superior switch performance, such as when using ripple carry adder. There is also the possibility of a low operation, which may operate at Low wattage Electronic designs for high-performance and small devices have become increasingly dependent on the use of VLSI circuits. The power of a processor is determined in large part by the multiplier used in its design. Multiplier factor booth coding is being used to reorder the input bits in order to reduce facility use. The booth decoder works by rearranging the specified booth equivalent. The Booth decoder has the ability to expand the range of zeros. As a result, the power consumption of the design will be decreased even more. As soon as the input bit constant drops below zero, related rows or columns of an adder must be disabled, if possible.

Article Details

This work is licensed under a Creative Commons Attribution-NoDerivatives 4.0 International License.

References

V. Chaitali and P A. Lathiya, " Performance Comparison of Carry Save Adder at 180nm, 90nm and 45nm CMOS Technology," International Journal of Advanced Research in Computer Engineering & Technology, 2016, pp. 1414-1419.

Kumar, M. Kiran, Sai Anusha and G Rekha. “A Design of Low Power Modified Booth Multiplier.” (2018).

Gupta, Namrata. "Power aware & high speed booth multiplier based on adiabatic logic." International Journal of Innovations in Engineering and Technology (IJIET) 2.3 (2013): 297-303.

R Kalaimathil,"A Survey on Area Efficient Low Power High Speed Multipliers", International Journal for Research in Applied Science & Engineering Technology, 2017, pp. 2932-2941

J.Kaur, P.Shukla and N Kr. Gahlan, " FPGA Implementation of 4-Bit Multipliers," 2012 International Journal of Computer Science And Technology, 2012, pp. 484-487.

A. S. Prabhu and V. Elakya, "Design of modified low power booth multiplier," 2012 International Conference on Computing, Communication and Applications, 2012, pp. 1-6, doi: 10.1109/ICCCA.2012.6179166.

D. Govekar and A. Amonkar, "Design and implementation of high speed modified booth multiplier using hybrid adder," 2017 International Conference on Computing Methodologies and Communication (ICCMC), 2017, pp. 138-143, doi: 10.1109/ICCMC.2017.8282661.

M. Singh, A. K. Maurya, S. P. Singh and S. K. Balasubramanian, "6×6 booth multiplier implemented in modified split-path data driven dynamic logic," 2014 Students Conference on Engineering and Systems, 2014, pp. 1-4, doi: 10.1109/SCES.2014.6880117.

A. Rajawat and A. Marwah, "GDI implementation of low power modified booth multiplier," 2016 Symposium on Colossal Data Analysis and Networking (CDAN), 2016, pp. 1-5, doi: 10.1109/CDAN.2016.7570923.

Aravind Babu S, Babu Ramki S and Sivasankaran K, "Design and implementation of high speed and high accuracy fixed-width modified booth multiplier for DSP application," 2014 International Conference on Advances in Electrical Engineering (ICAEE), 2014, pp. 1-5, doi: 10.1109/ICAEE.2014.6838565.

S. Saravanan and M. Madheswaran, "Design of Hybrid Encoded Booth Multiplier with Reduced Switching Activity Technique and low power 0.13µm adder for DSP block in wireless sensor node," 2010 International Conference on Wireless Communication and Sensor Computing (ICWCSC), 2010, pp. 1-6, doi: 10.1109/ICWCSC.2010.5415884.

B. Gowridevi, B. Gangadevi, A. V. Geethamani, T. Pavithra and S. R. Kumar, "Modified booth multiprecision multiplier with scalable voltage and frequency units," 2014 IEEE International Conference on Computational Intelligence and Computing Research, 2014, pp. 1-5, doi: 10.1109/ICCIC.2014.7238421.

M. J. Rao and S. Dubey, "A high speed and area efficient Booth recoded Wallace tree multiplier for fast arithmetic circuits," 2012 Asia Pacific Conference on Postgraduate Research in Microelectronics and Electronics, 2012, pp. 220-223, doi: 10.1109/PrimeAsia.2012.6458658.

W. He, C. Liu, W. Liu and Y. Chen, "A high accuracy fixed-width Booth multiplier using select probability estimation bias," 2014 4th IEEE International Conference on Information Science and Technology, 2014, pp. 385-388, doi: 10.1109/ICIST.2014.6920408.

S. Sri Sakthi and N. Kayalvizhi, "Power aware and high speed reconfigurable modified booth multiplier," 2011 IEEE Recent Advances in Intelligent Computational Systems, 2011, pp. 352-356, doi: 10.1109/RAICS.2011.6069333.

. T. Kukade, R. B. Deshmukh and R. M. Patrikar, "A Novel Parallel Multiplier for 2's Complement Numbers Using Booth's Recoding Algorithm," 2014 International Conference on Electronic Systems, Signal Processing and Computing Technologies, 2014, pp. 93-98, doi: 10.1109/ICESC.2014.103.

R. Prathiba, P. Sandhya and R. Varun, "Design of high performance and low power multiplier using modified booth encoder," 2016 International Conference on Electrical, Electronics, and Optimization Techniques (ICEEOT), 2016, pp. 794-798, doi: 10.1109/ICEEOT.2016.7754795.

K. D. Rao, C. Gangadhar and P. K. Korrai, "FPGA implementation of complex multiplier using minimum delay Vedic real multiplier architecture," 2016 IEEE Uttar Pradesh Section International Conference on Electrical, Computer and Electronics Engineering (UPCON), 2016, pp. 580-584, doi: 10.1109/UPCON.2016.7894719.

B. M. Pranay and S. Jandhyala, "Accuracy Configurable Modified Booth Multiplier Using Approximate Adders," 2015 IEEE International Symposium on Nanoelectronic and Information Systems, 2015, pp. 281-285, doi: 10.1109/iNIS.2015.50.