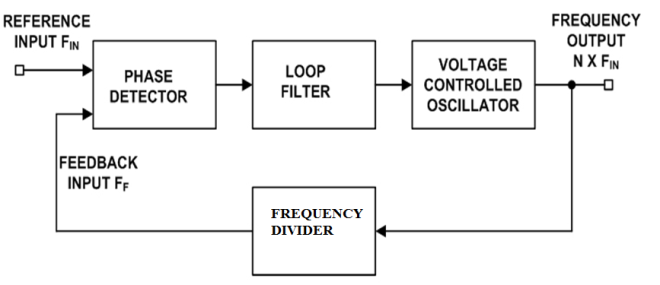

Design of Frequency Divider (FD/2 and FD 2/3) Circuits for a Phase Locked Loop

Main Article Content

Abstract

This paper reports on three design of Frequency Divider (FD/2) and Frequency Divider (FD 2/3) circuits. Tanner EDA tool developed on 130nm CMOS technology with a voltage supply of 1.3 V is used to build, model, and compare all circuits. For the FD/2 circuit, E-TSPC Pass Transistor logic uses 1.77 µW, whereas TSPC logic consumes 5.57 µW for the FD 2/3 circuit. It implies that the TSPC logic is the best solution since it meets the speed and power consumption requirements.

Article Details

This work is licensed under a Creative Commons Attribution-NoDerivatives 4.0 International License.

References

M. Fujishima et al., “Low-power 1/2 frequency dividers using 0.1µm CMOS circuits built with ultrathin SIMOX substrates,” IEEE J. Solid-State Circuits, vol. 28, pp. 510–512, April 1993.

.S.Pellegrino, S. Levantino, Member, IEEE, C. Samori, Member, IEEE, and A. L. Lacaita, Senior Member, IEEE, “A 13.5-mW 5-GHz Frequency Synthesizer With Dynamic-Logic Frequency Divider”, IEEE journal of solid-state circuits, vol. 39, no. 2, Feb 2004.

.Jianhua Lu, Ning-Yi Wang, and Mau-Chung Frank Chang, IEEE, “A Compact and Low Power 5–10 GHz Quadrature Local Oscillator for Cognitive Radio Applications,”IEEE Journal of solid-state circuits, vol. 47, no. 5, may 2012

Vamshi Krishna Manthena, Manh Anh Do, Chirn Chye Boon, and Kiat Seng Yeo, “A Low-Power Single-Phase Clock Multiband Flexible Divider’,IEEE Transactions on very large scale integration (vlsi) systems, vol. 20, no. 2, February 2012.

Yin-Tsung Hwang and Jin-Fa Lin, “Low Voltage and Low Power Divide-By-2/3 Counter Design Using Pass Transistor Logic Circuit Technique”, IEEE transactions on very large scale integration (vlsi) systems, vol. 20, no. 9, September 2012.

B. Razavi, K.F. Lee, R.-H. Yan, “A 13.4-GHz CMOS frequency divider,” IEEE International Solid-State Circuits Conference, pp.176-177, Feb.1994.

J. Yuan and C. Svensson, “High-speed CMOS circuit technique,” IEEE J. Solid-State Circuits, vol. 24, no. 2, pp. 62–70, 1989.

U. Kumar, G. Kavya, J. Kishore and K. A. N. Raj, "BL-CSC Converter Fed BLDC Motor Drive with Sensorless Control," 2018 4th International Conference on Electrical Energy Systems (ICEES), 2018, pp. 449-453, doi: 10.1109/ICEES.2018.8443286.

G. Kavya, P. Kaarthika, S. Jeevitha and U. A. Kumar, "Improved power quality converter fed BLDC motor drive," 2017 International Conference on Innovations in Information, Embedded and Communication Systems (ICIIECS), 2017, pp. 1-5, doi: 10.1109/ICIIECS.2017.8276005.